PCB设计中的十大EMC挑战

来源:智芯Player

发布时间:2025-11-12

设计印刷电路板(PCB)本身就面临着尺寸限制、结构集成、热管理及功率效率等多重挑战。在此之 上,电磁兼容性(EMC)问题为新产品的上市带来了更多障碍,进一步增加了设计的复杂性。

电磁兼容性(EMC)涉及广泛的电磁现象,涵盖了电磁能量的意外生成、传播与接收。EMC问题不仅可能妨碍您的电路板正常运行,还可能对周围的其他电子系统造成干扰。不同领域的产品有对应的EMC标准,但是整体来说都是大同小异,处理策略以及面临的问题都有类的对应之策。

本文旨在探讨PCB设计中最常见的EMC问题,并提供切实可行的策略以降低PCB设计本身对板级EMC的影响。

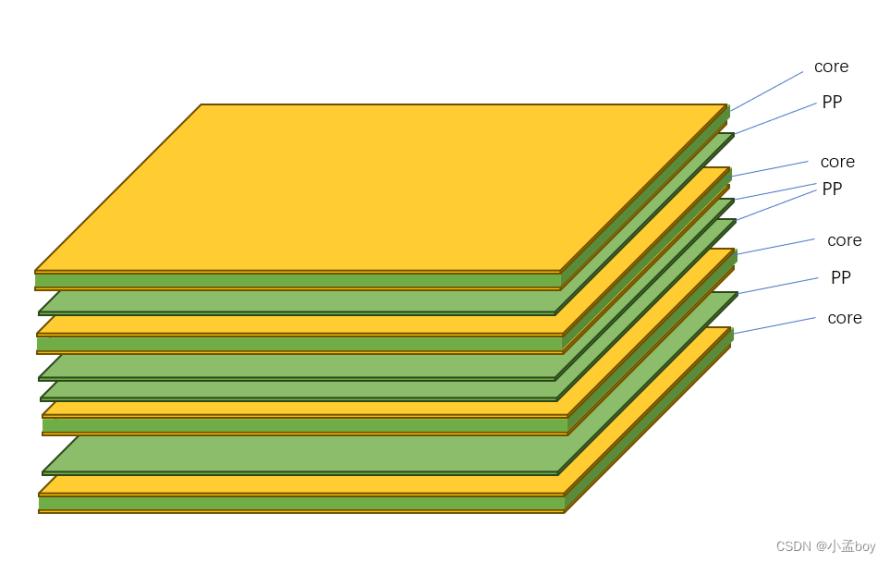

电路板层叠结构 (Board Stack-Up)

电路板的层叠结构定义并排列了PCB内部的导电层与绝缘层。这些层的属性定义如下:

导电层 (Conductive layers): 数量、顺序、材料和铜厚 (copper weight)。

绝缘层 (Non-conductive layers): 数量、顺序、介电材料和厚度 (height)。

PCB的设计范围可以从基础的单层板,到非常复杂的多层系统。由于对高频信号和元器件小型化的需求日益增长,当今大多数PCB都采用4层或更多层的设计。

对这些层进行合理的排布,可以为PCB的EMC(电磁兼容性)和信号完整性性能带来诸多益处。这使得层叠结构设计成为新PCB设计中最关键的决策之一。

精心规划层叠结构——包括合理的层序、接地和屏蔽——可以最大限度地减少串扰和阻抗失配。在PCB设计周期的后期修改层叠结构,会非常困难且耗时。因此,在设计的早期阶段就确定一个稳健的PCB层叠结构方案,可以为您节省大量的时间和精力。

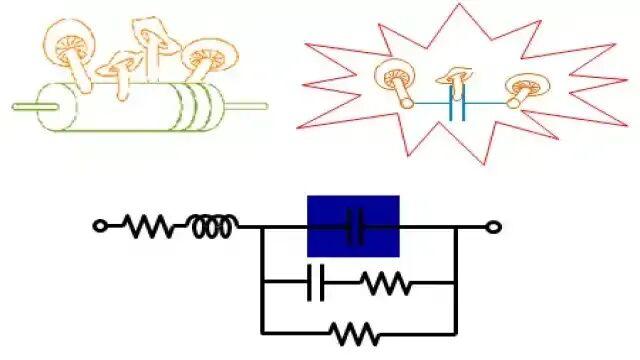

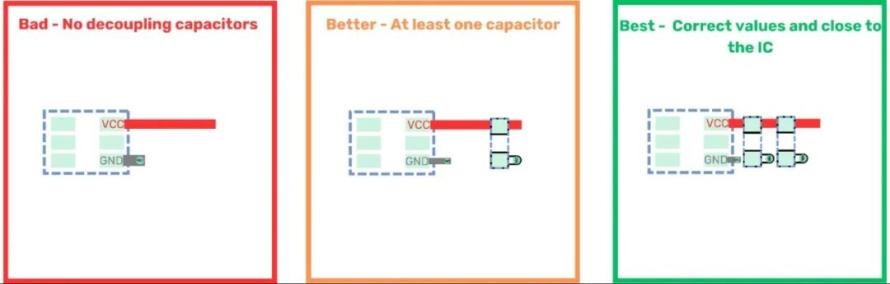

寄生阻抗 (Parasitic Impedance)

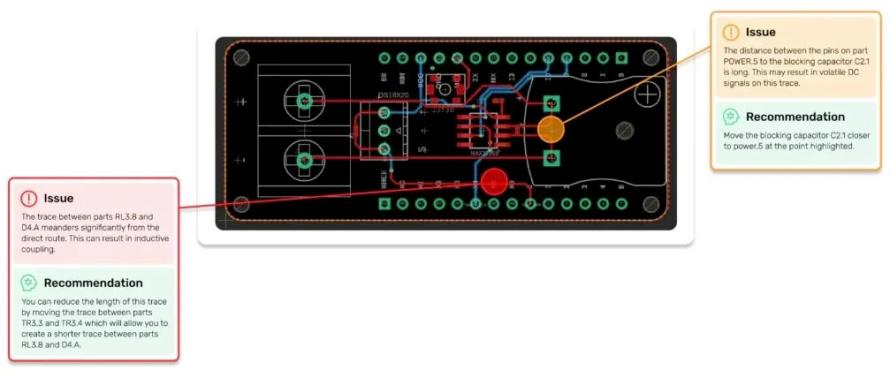

PCB走线天然就具有一定的电阻、电感和电容。这种并非设计所需的、意外形成的阻抗,就是所谓的寄生阻抗。将这种有害阻抗降至最低,对于保证信号完整性(Signal Integrity)和电磁兼容性(EMC)而言至关重要。

在您的PCB设计中,可以通过采用短而宽的元器件间走线来减小寄生阻抗。此外,合理的元器件布局也起着关键作用。

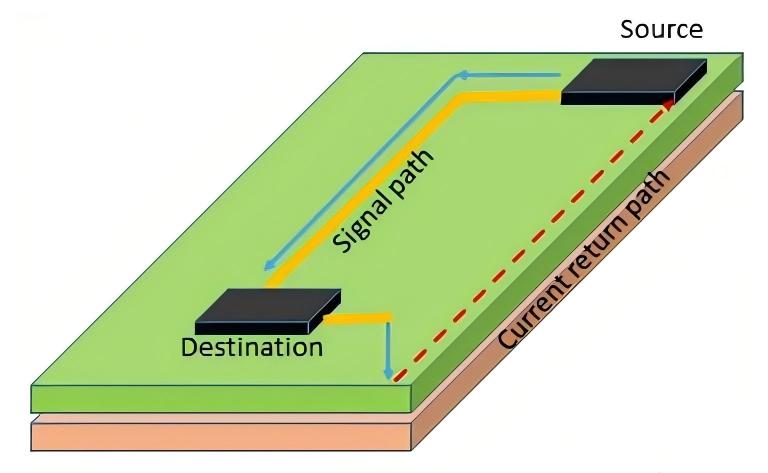

回流路径 (Return Paths)

所有电流都会从源端流出并返回源端,形成一个完整的电路回路。回流电流总是会选择阻抗最低的路径。在低频时,这条路径由最低的电阻决定;而在中高频时,回流电流则会沿着电感最小的路径流动。

为了避免不必要的电磁辐射和耦合,回流路径需要尽可能地短。这可以通过遵循以下基本准则来实现:

让元器件之间的距离尽可能近;特别是那些驱动快速上升沿信号(short rise times)的元器件。

使用大面积的接地平面(地平面),以尽可能降低电感。

采用能够缩短回流路径的电路板叠层设计。

避免在地平面上出现分割或缝隙。

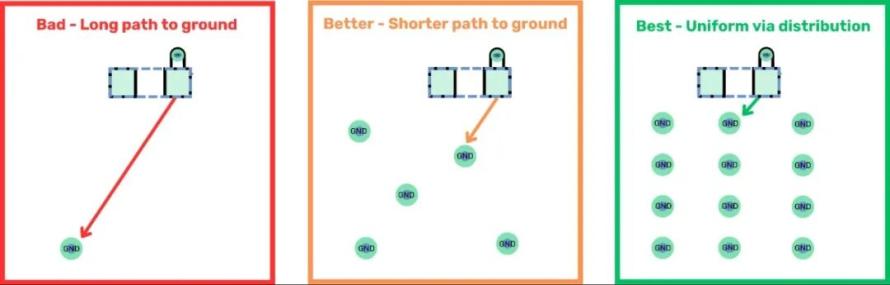

接地连接与参考平面 (Ground Connections and Reference Planes)

“地”(Ground)为电信号提供了一个稳定的参考点。如果通过很长的走线或质量不佳的铜平面连接到地,就会直接引入非预期的寄生效应。

为电流提供一条短的回地路径,可以确保实现低阻抗的回流路径。这也能最大限度地减少形成“地环路”(Ground loops)的可能性,而地环路会产生辐射发射(radiated emissions),并恶化信号完整性(Signal Integrity)和电磁兼容性(EMC)。

参考平面(Reference planes)是指大面积的铜箔区域,它们的作用是为接地电流提供回流路径,并为高频信号提供参考基准。参考平面是传输线设计所必需的,并且是一种控制电磁辐射的高效且经济的解决方案。

我们经常看到PCB的不同层上都铺有大面积的铜箔区域。然而,这些铜箔区域的阻抗并非为零,因此它们会引入电感、电容和电阻。为了最大限度地减小这种非理想阻抗的影响,回流路径在电气意义上必须尽可能短。这也意味着,在设计不同PCB层上的地平面之间的连接时,也必须确保其低阻抗特性。

缝合过孔 (Stitching Vias)

可以通过使用缝合过孔来实现(参考)平面间的低阻抗。通过沿着参考平面均匀地布设过孔,可以大幅降低它们之间的阻抗,进而减少寄生效应。

这项技术最大的优点在于,它并不会增加PCB的成本或制造复杂性。

串扰 (Crosstalk)

将长走线彼此靠得太近,会对信号完整性(Signal Integrity)和电磁兼容性(EMC)产生负面影响。由一条走线产生的电磁场会与相邻走线相互作用,从而导致不必要的信号耦合。这种现象就是所谓的串扰。

为了减少串扰:

增加相邻走线之间的距离。

减小走线与参考平面之间的距离。

在信号层之间增加地平面以约束电磁场(起到屏蔽作用)。

虽然第一种方法易于实现,但它可能会增大电路板的尺寸。而第二种方法则可能对PCB的其他方面产生显著影响,例如制造工艺或高速走线的阻抗控制。

处理串扰的其他技术还包括:避免走线长时间平行布设、将元器件放置在远离I/O(输入/输出)互连接口的位置,以及将高噪声发射源隔离到板叠(stack-up)的不同层中。

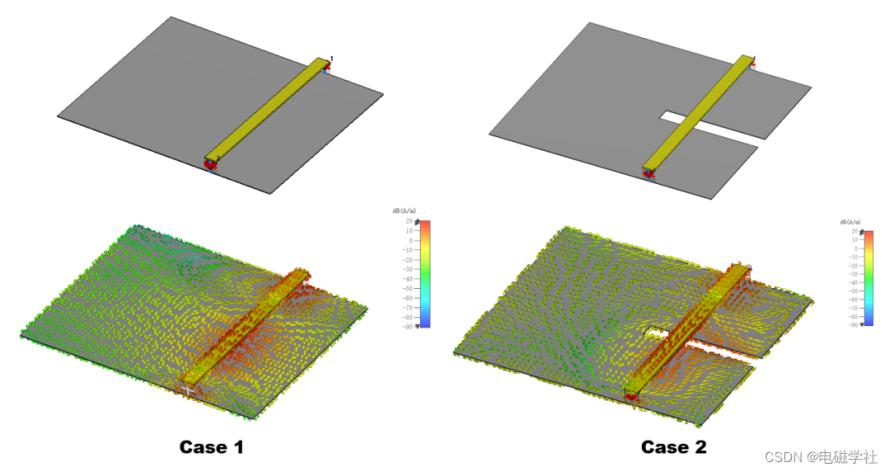

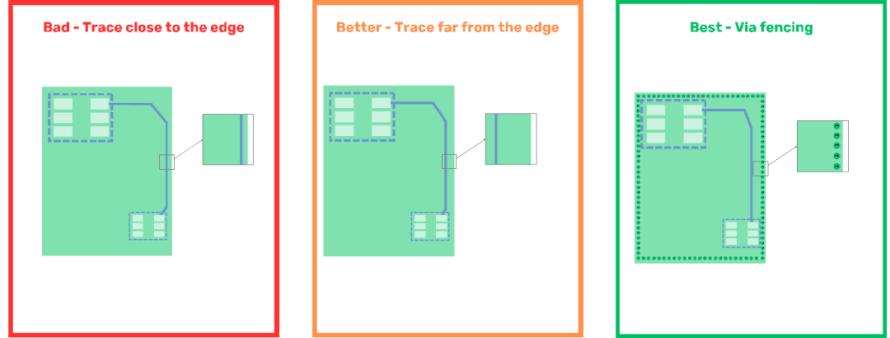

靠近电路板边缘的走线 (Traces Close to the Board Edges)

传输高速数字信号的走线会产生高强度的交变场。如果这些走线距离一个没有屏蔽的电路板边缘太近,这些场就可能会逸出电路板,从而产生非预期的辐射发射(radiated emissions)。

假设电路板有一个完整的参考平面,请遵循以下准则来减少非预期的辐射:

将走线向电路板内部移动。

在整个电路板周围增加一圈过孔栅栏(via fence)以进行屏蔽。

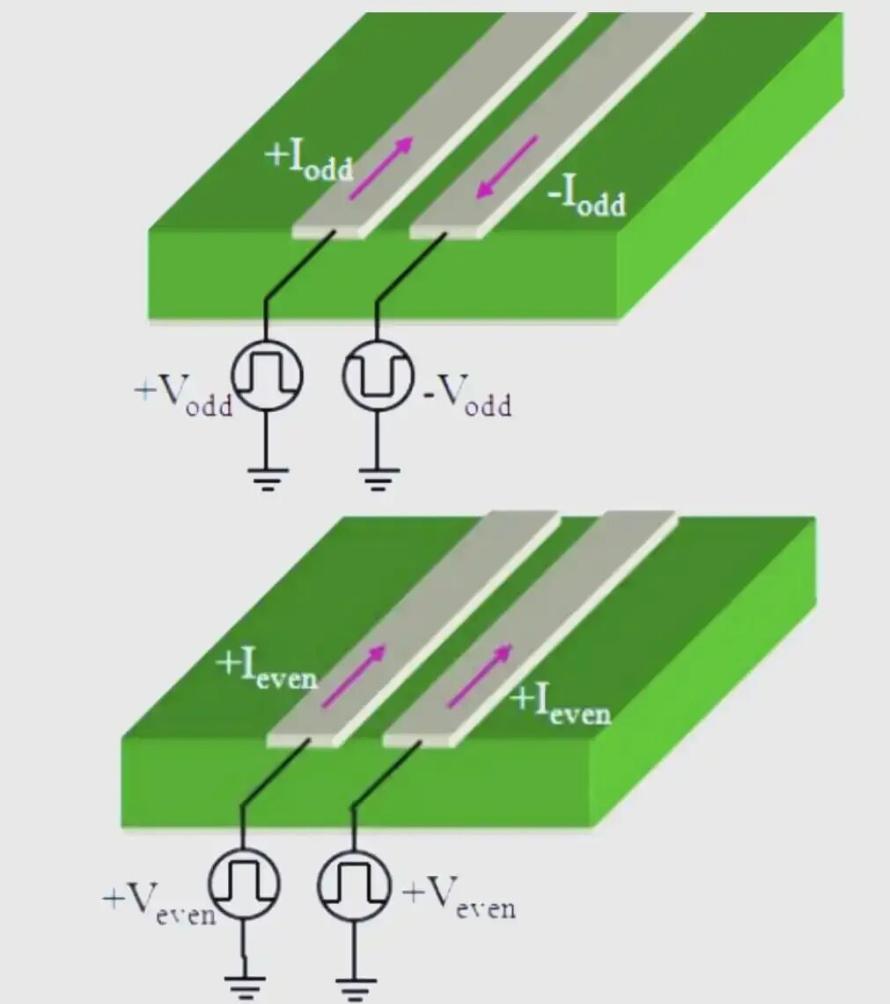

差分阻抗 (Differential Impedance)

差分对(Differential pairs)是一种特殊的传输线,其两条信号线以平行方式布线。为避免信号反射,差分对布线时需要保持恒定的阻抗;为避免信号偏斜(signal skew),则需要保持等长。

为了有效控制差分阻抗:

通过合理选择介电层(dielectric)的厚度及其特性来控制电路板的叠层结构(stackup)。

在差分对附近放置完整的地平面。

只有当参考(地)平面位于信号线的下方时,用于计算传输线阻抗的公式才是有效的。如果缺少地平面或地平面上存在间隙(gap),将会导致阻抗不匹配,从而产生信号损耗和反射。

免责声明

- 1、本文内容版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系感算商城(service@gansuan.com),我方将及时处理。

- 2、本文的引用仅供读者交流学习使用,不涉及商业目的。

- 3、本文内容仅代表作者观点,感算商城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

- 4、如需转载本方拥有版权的文章,请联系感算商城(service@gansuan.com)注明“转载原因”。未经允许私自转载感算商城将保留追究其法律责任的权利。