选择性波峰焊连锡难题的终极解决方案

来源:埃斯特磁

发布时间:2025-10-24

在电子制造领域,连锡问题如同悬在工程师头顶的达摩克利斯之剑——当0.3mm间距的Type-C接口出现焊点桥接,整块手机主板可能面临报废。传统波峰焊的连锡缺陷率高达2000PPM,而AST埃斯特的选择性波峰焊技术如何将这一数字压缩至500PPM以下?

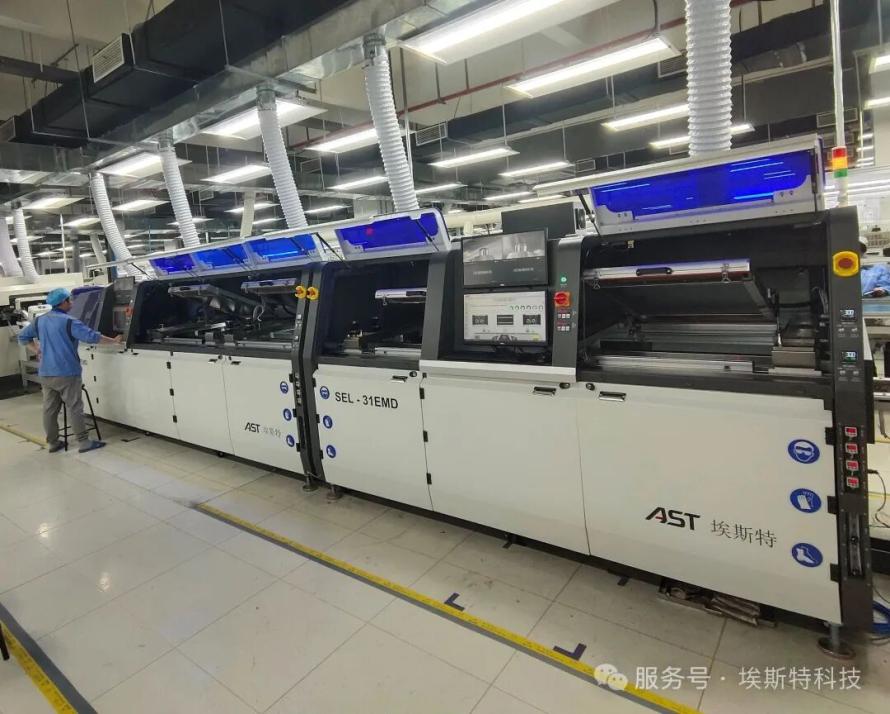

AST埃斯特四缸八头选择性波峰焊

连锡根源的精准狙击战

助焊剂作为焊接过程的"隐形守护者",其活性不足或喷涂不均直接导致熔锡表面张力失控。AST埃斯特的解决方案直击要害:采用氮气保护工艺配合智能喷涂系统,使助焊剂覆盖均匀度提升至98%,氧化率降低70%。某汽车ECU制造商实测显示,将预热温度精确控制在110℃、喷量增加15%后,热敏元件连锡率从5%骤降至0.3%。

温度与速度的黄金配比同样关键。当锡炉温度低于265℃或运输速度偏离1.2m/min标准值时,焊接缺陷率呈指数级上升。AST埃斯特第五代伺服控制系统实现了250-300℃无级调温,配合20mm/s的拖焊速度,使40pin排针焊接合格率达到99.97%。

从设计端破解焊盘困局

PCB设计缺陷是连锡的隐形推手。当焊盘间距小于0.4mm且缺乏阻焊坝时,AST埃斯特的载具展现出独特价值:其±0.05mm的定位精度可强制修正PCB变形,而动态锡嘴系统能以0.1mm精度实施脉冲点焊,将热影响区压缩至1.5mm内。某服务器厂商应用该方案后,PCIe插槽透锡率实现100%突破。

针对IC与排插密集布局的"死亡区域",倾斜7度进板策略成为破局关键。这种角度设计使熔锡自然分离,配合1.2秒/点的焊接节奏,成功解决LCP天线模块的桥接难题。数据显示,采用该工艺的5G基站主板良品率提升23%。

随着微型化焊接精度进入微米时代,选择性波峰焊已从备选工艺升级为核心生产力。AST埃斯特通过300+企业验证的解决方案证明:当精准控制与智能算法深度融合,连锡难题终将成为历史注脚。

免责声明

- 1、本文内容版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系感算商城(service@gansuan.com),我方将及时处理。

- 2、本文的引用仅供读者交流学习使用,不涉及商业目的。

- 3、本文内容仅代表作者观点,感算商城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

- 4、如需转载本方拥有版权的文章,请联系感算商城(service@gansuan.com)注明“转载原因”。未经允许私自转载感算商城将保留追究其法律责任的权利。