芯片设计流程详解

来源:鲜枣课堂

发布时间:2025-06-26

芯片分为数字芯片、模拟芯片、数模混合芯片等多种类别。不同类别的设计流程也存在一些差异。

接下来,我们就以数字芯片为例,详细看看芯片到底是如何设计出来的。

█ 芯片设计的主要流程

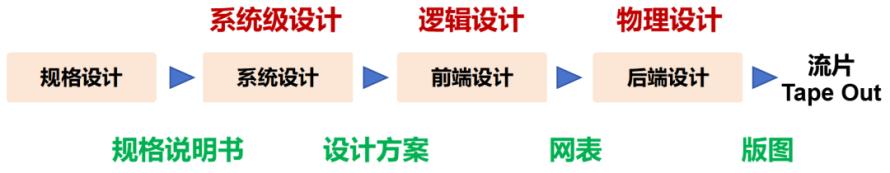

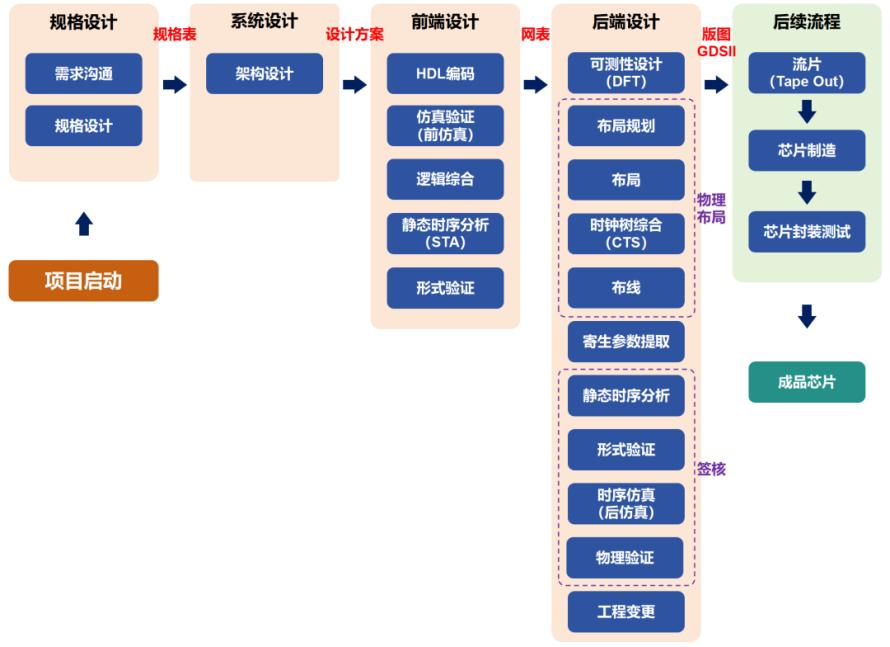

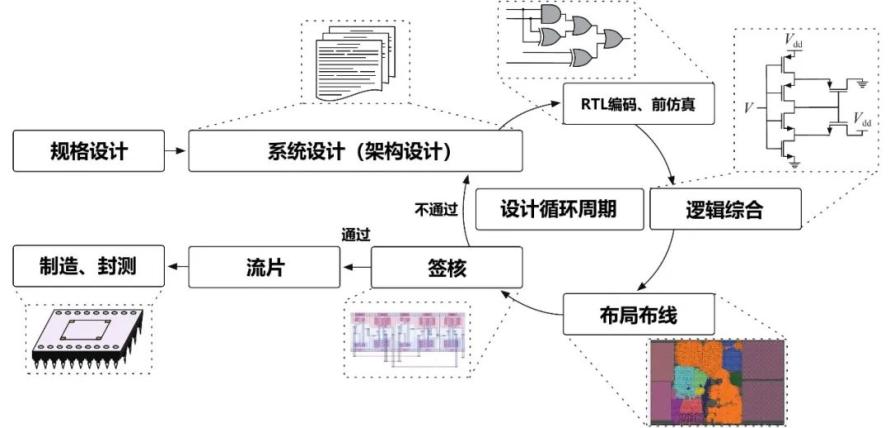

芯片的设计,总体分为规格定义、系统设计、前端设计(Front-End Design) 和后端设计(Back-End Design)四个阶段。

网上有些资料为了简单,也会将规格定义和系统设计也归入前端设计。

上篇文章小枣君给大家说过,现在主流的芯片设计思路是自顶向下(Top-Down),也就是“先宏观,再微观”。

简单来说,就是先做芯片整体设计(功能、接口、模块),再做各个模块的设计。做模块设计的时候,先设计逻辑原理(写代码),然后再用EDA工具转化为逻辑电路图(网表),最后再设计物理电路图(版图)。

整个过程,穿插着大量的“设计-验证(仿真)-设计-验证(仿真)”循环。需要确保每一步都准确无误,才会进入下一步。

四大阶段中,前端设计,就是逻辑设计。主要是将芯片的功能需求转化为可实现的电路逻辑,确保功能正确性,不考虑物理实现细节。

后端设计,则是物理设计,专注于物理实现,将前端的设计转化为实际的版图。这个阶段需要脚踏实地,考虑制造工艺约束、信号完整性、功耗管理等实际问题,解决物理实现的工艺挑战。

前端设计和后端设计的各个子阶段如下图所示:

接下来,我们分别进行介绍。

█ 规格定义

芯片设计的第一步,是搞明白自己到底要做一款什么样的芯片。

这不是领导拍脑袋决定的,而是需要芯片设计团队和客户(甲方)以及利益相关方进行充分沟通,了解具体设计需求之后确定的。

需求包括:到底要实现什么功能,用于什么环境,算力、成本、功耗大概是多少,需要提供哪些接口,需要遵循什么安全等级,等等。

所有的需求会转化为芯片的基本参数,最终以Spec(芯片规格说明书)文件的形式进行记录。芯片设计的基本要求,就此确定。

█ 系统设计

接下来,就要由架构工程师出马了。

架构工程师要根据规格Spec,设计具体的实现方案。包括但不限于:整个芯片的架构、业务模块、供电、接口、时序、性能指标、面积和功率约束等。

芯片的架构主要由芯片的类别和功能所决定。

如果芯片主要用于通用计算和数据处理,冯・诺依曼架构可能是一个合适的选择。如果侧重于高速的数据处理和实时性要求高的应用,如数字信号处理或一些特定的嵌入式系统,哈佛架构可能更具优势。

对于复杂的芯片设计,还可能采用多核架构或异构集成架构(混搭)。

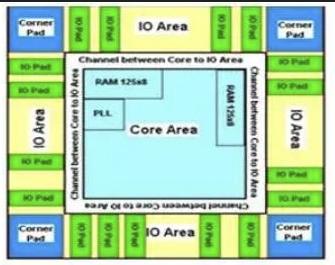

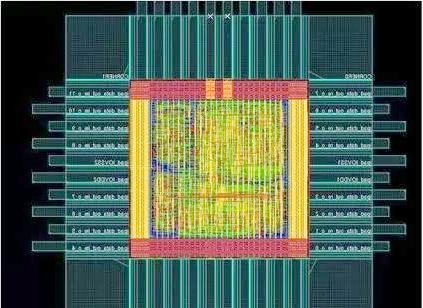

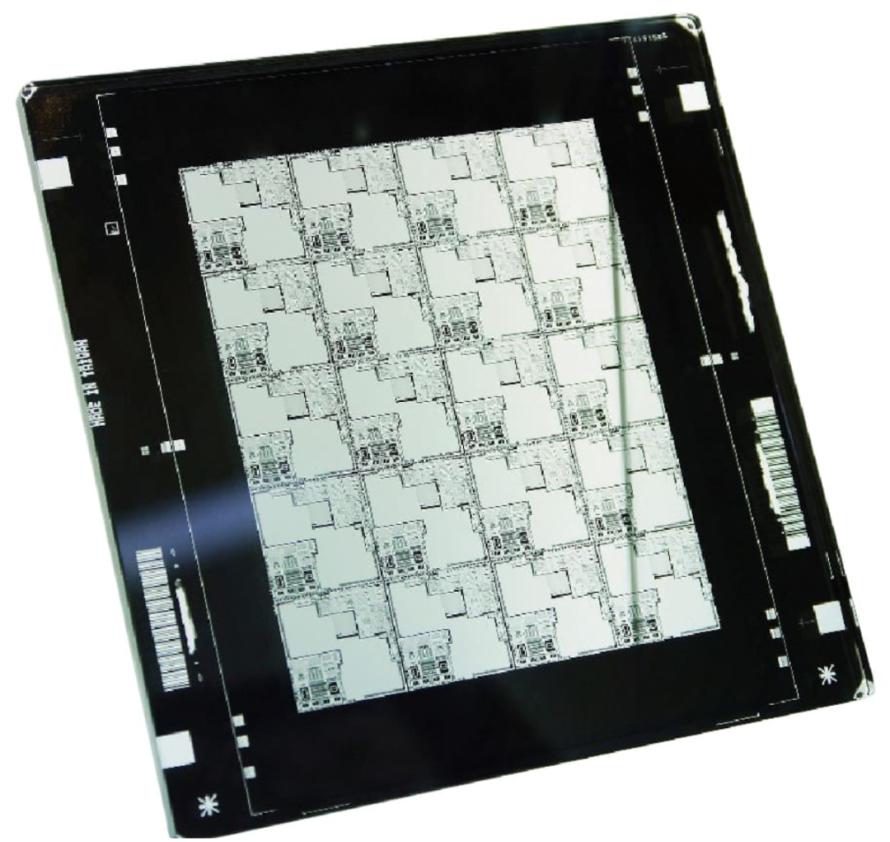

芯片的整体布局(示例)

选定架构之后,架构师还要在细节上进行优化和创新。例如调整各个功能模块之间的连接方式、优化数据通路以减少延迟,或者采用新的计算模式,等等。

架构师还要确定哪些功能可以用软件实现,哪些部分需要用硬件实现。上篇小枣君介绍过IP核,哪些部分要采购IP核,哪些部分自己做,也是由架构师决定的。

█ 前端设计(逻辑设计)

好了,开始进入前端设计部分了。我们保持耐心,一步一步来看。

· HDL编码

首先,是进行HDL(Hardware Description Language,硬件描述语言)编码。

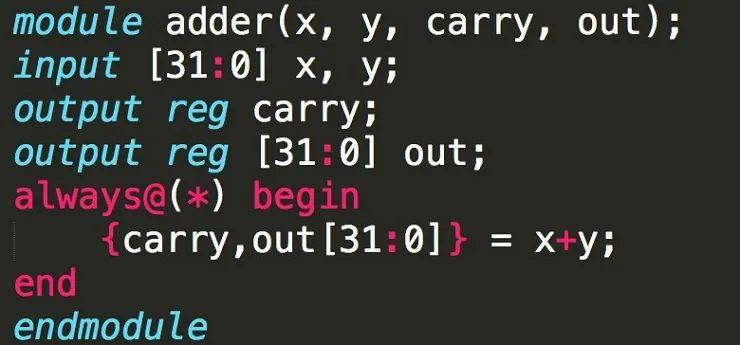

架构设计方案完成后,芯片设计工程师将根据方案,针对各模块进行具体的电路设计。他会使用专门的硬件描述语言(Verilog或VHDL),对具体的电路实现进行RTL(Register Transfer Level,寄存器传输级)级别的代码描述。

简单来说,就是用代码来表述芯片的逻辑功能和数据传输。

Verilog作为一种常用的硬件描述语言,能够对电路(系统)进行多层次描述,包括系统级、算法级、寄存器传输级(RTL级)、门级和开关级。在数字IC设计流程中,RTL级描述最为关键和常用。因此,Verilog代码也常被称作RTL代码。

Verilog代码范例(32位加法器)

需要注意的是,HDL编码需要结合晶圆厂提供的库(libaray)和器件(device)等基础资源来设计。有些芯片设计工程师也会基于晶圆厂提供的资源,进行底层优化设计。

· 仿真验证

HDL编码完成之后,就要开始第一波验证(Verification)了。

前面我说过,芯片设计几乎每一步都要进行验证或仿真,就是为了确保不出错,因为出错的代价实在太大。

这一步的仿真验证,主要包括电路逻辑功能方面的验证,也就是证明设计的功能是否符合设计规格中的定义,是否存在逻辑实现错误。

如果发现错误,就需要返回上一步,进行修改,甚至要返回方案设计阶段进行修改。修改之后,再重新进行验证。

验证方法包括:(借助工具)通过在搭建的验证环境中输入激励(就是加输入信号),然后看检测输出波形是否和预期一样,以此来进行判断。

验证仿真的工具主要包括VCS、Qustasim等EDA工具(进行编译和仿真),以及Verdi等工具(进行debug)。

需要注意的是,这个阶段的仿真,也被称为“前仿真”。待会我们还有一个“后仿真”。

“前仿真”是在理想状态下进行的。它基于理想化的抽象模型,忽略物理延迟和布线细节,专注于功能正确性。

· 逻辑综合

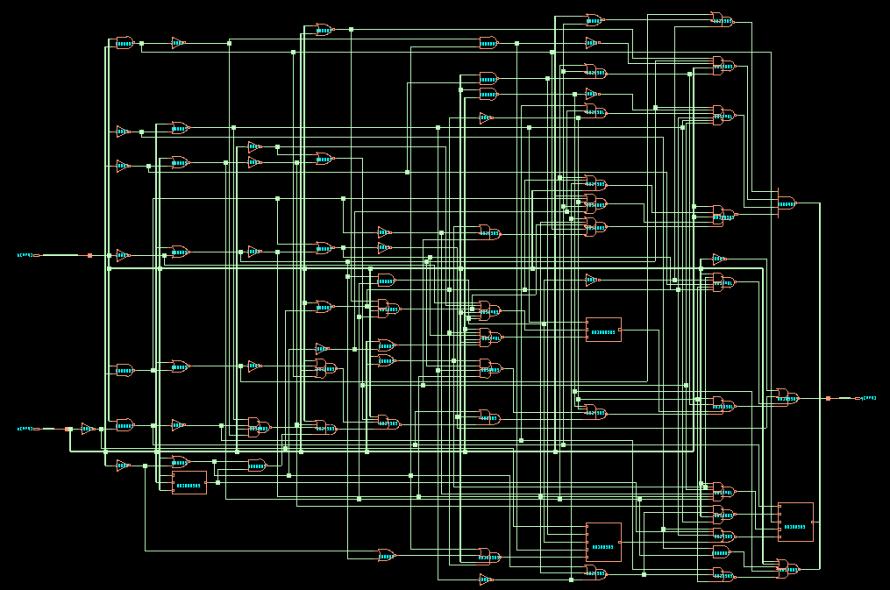

接下来,验证工程师要使用一些EDA工具,将RTL代码翻译成门级网表(Gate level Netlist),也就是实际的逻辑门电路(也包含了逻辑结构和连接关系,也是后端设计的关键输入)。

门级网表的样例

这个步骤就是逻辑综合(Synthesis),有时候直接简称“综合”。

逻辑综合主要包括翻译、优化、映射步骤。

翻译:先将Verilog/VHDL代码转换为工艺无关的、初级的、未优化的通用门级电路。

优化:逻辑综合需要设定约束条件,也就是希望逻辑综合出来的电路在面积、时序、时延等(PPA)目标参数上达到的标准。优化,是根据约束条件和工艺库(由晶圆厂提供)参数,进行逻辑结构调整,去掉冗余单元,以此满足要求。

映射:最终,将门级逻辑电路映射到的工艺库上。

需要注意的是,不同晶圆厂的工艺库,门电路基本标准单元(standard cell)的面积、时序参数是不一样的。所以,选用的库不一样,综合出来的电路在面积、时序上就不一样。

· 静态时序分析

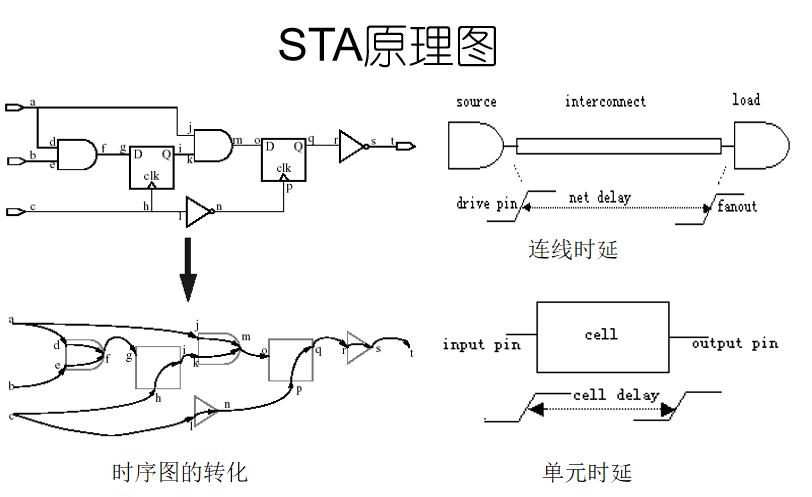

静态时序分析(Static Timing Analysis,STA),也属于验证的范畴,主要是在时序上对电路进行验证。

具体来说,是在不提供激励的情况下,验证设计时序特性,检查电路是否存在建立时间(setuptime)和保持时间(holdtime)的违例(violation)。

在数字电路中,一个寄存器如果出现前面说的违例,就无法正确采样数据和输出数据。所以,以寄存器为基础的数字芯片功能,就会出现问题。

首先,它能帮助我们确定芯片的最高工作频率。

通过详细的时序分析,工程师可以更好地控制工程的各个环节,从而减少延迟,尽可能地提升芯片的工作频率。

芯片的最高工作频率由网表(netlist)的关键路径决定。关键路径是网表中信号传播时延的最长路径。

其次,静态时序分析也是检查时序约束是否满足的重要手段。

在时序分析的过程中,我们可以查看目标模块是否满足预设的约束条件。如果不满足,分析结果将帮助我们精确地定位到问题点,并给出详细的改进建议。

最后,静态时序分析还能用于分析时钟质量。

时钟信号存在抖动、偏移和占空比失真等缺陷。通过时序分析,我们可以有效地验证这些缺陷对目标模块性能的影响。

STA工具,包括Synopsys的PT(Prime Time)工具等。

它可以分为三个基本步骤:

1、将netlist看成一个拓扑图;

2、进行时延计算(连线时延net delay、单元时延cell delay);

3、找到关键路径,并计算时延,进行判断。

· 形式验证

这一步也是验证,是从功能上对逻辑综合后的网表(netlist)进行验证。

形式验证主要通过数学手段来完成,不考虑工艺因素,无需激励或时序检查即可进行。

在形式验证中,等效性检查(也叫等价性检查)是一种常用方法。

它通过将当前设计与已知的黄金设计(功能验证后的HDL设计)进行对比,来确认设计的功能等效性,确保逻辑综合过程中没有改变原先HDL描述的电路功能。

覆盖率,是评估验证充分性的一个关键指标。它主要分为两大类:代码覆盖率和功能覆盖率。

代码覆盖率,旨在检查RTL代码是否冗余,并确保设计要点得到全面遍历。

功能覆盖率,专注于检查自定义container(容器)中的功能是否被充分测试。

在前端设计的最后阶段,需要完成代码覆盖率的充分性审查。对于未达到100%覆盖率的情况,需要给出合理解释,以确保芯片功能不受影响。

以上验证工作都完成后,前端设计(逻辑设计)就基本完成了。

几个主要阶段的输入和输出,如下表所示:

█ 后端设计(物理设计)

前端设计的结果,是得到了芯片的网表(netlist)电路。

不同的EDA工具,生成的网表文件的文件格式也不太一样。例如*.v(Design Compiler,Synopsys公司)、*.vh(PKS,Cadence公司)和*.edf(Synplify,Synplicity公司)。

后端设计,是要基于网表,制作出物理版图。

具体来说,是先基于网表,在给定大小的硅片面积内,对电路进行布局规划(Floor Plan)、布局(Place)和布线(Route)。

然后,再对物理版图进行功能和时序上的各种验证(DRC、LVS、ERC等)。

最后,生成用于制造光掩模版和流片的GDS(Geometry Data Standard)版图。

整个过程有点像制作PCB电路板。当然,复杂度要高出无数倍。

接下来,我们来看每个步骤:

· 可测性设计

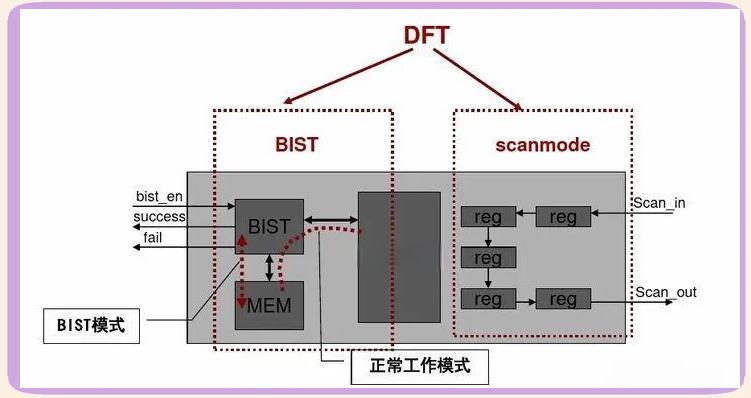

可测性设计(Design for Test,DFT),是为了方便后续对芯片进行测试,提前进行的自带测试电路设计。

现在的芯片都很复杂,出现问题的话,往往很难查找原因。可测试性设计就是为将来找问题进行提前考虑。

可测性设计的常见方法,是在设计中插入扫描链、内建自测试(BIST)、边界扫描单元等特殊架构,将非扫描单元(如寄存器)变为扫描单元,提升电路内部信号控制与观测能力。

DFT示例图

在测试时,在Scan-In阶段加载激励信号,在Capture阶段捕获组合逻辑响应,最终通过Scan-Out移出比对,就能得出结果。

可测性设计技术的基础评价指标包括可控性和可观测性。具体情况可以另行搜索网上资料,限于篇幅就不多介绍了。

注意,在有些文献里,也会将可测性设计归为前端设计的范畴。

· 物理布局

可测性设计之后,就要开始进行物理布局(layout)了。

物理布局是芯片设计流程中从逻辑视图向物理视图的转换过程。

它需要考虑到元件的尺寸、形状、相互之间的间距,以及连线的长度和宽度等各种复杂因素。布局的好坏,直接影响到芯片的信号抗干扰能力、寄生电容和电感的大小,决定了芯片的整体性能和可靠性。

好的物理布局,是要实现空间利用率、总线长度、时序的完美平衡。也就是说,空间利用率要尽量高,总线要尽量短,时序要尽量收敛。

物理布局的主要步骤包括:布局规划、布局、时钟树综合、布线等。我们逐一来看:

· 物理布局之 布局规划

这个步骤没有标准的最佳方案,但又有很多细节需要考量。

设计者需要根据电路的功能和性能要求,以及硅片的尺寸和工艺约束,来安排电路元件的位置。例如,设计者可能需要将高速或者热敏感的电路部分放在芯片的中心位置,以便获得更好的性能和热分布。

在布局规划的过程中,同样要紧密结合晶圆厂的资料来。例如,晶圆厂提供的PDK(Process Design Kit,工艺设计套件)。

PDK包含了工艺相关的各种参数和模型,比如晶体管尺寸、层间距、金属氧化层厚度等,就连线宽、线距等设计规则都与之相关。如果脱离PDK,你设计的东西,人家根本生产不了,就是白搭。

· 物理布局之 时钟树综合

时钟树综合(Clock Tree Synthesis,CTS),简单说就是时钟的布线,构建时钟网络。

前面说了,时钟信号在数字芯片中起到了全局指挥的作用。我们在布放时钟线的时候,需要对称式地连接到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。(时钟偏差通常需控制在时钟周期的10%以内。)

· 物理布局之 布线

这里的布线(Routing),就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。

在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束条件下,需要对信号线进行合理规划,将各单元和I/O pad(输入/输出焊盘管脚)连接起来。

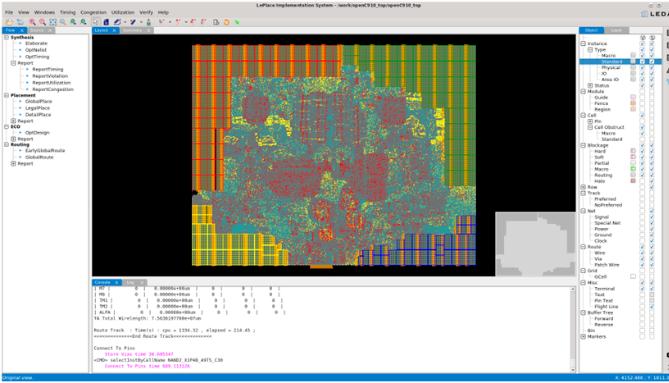

布线工具界面

设计者需要根据信号的频率和时序要求,以及工艺的布线规则,来安排信号线的路径和层次。例如,设计者可能需要使用多层金属线来实现复杂的信号交叉,或者使用特殊的布线技术来降低信号的传播延迟。

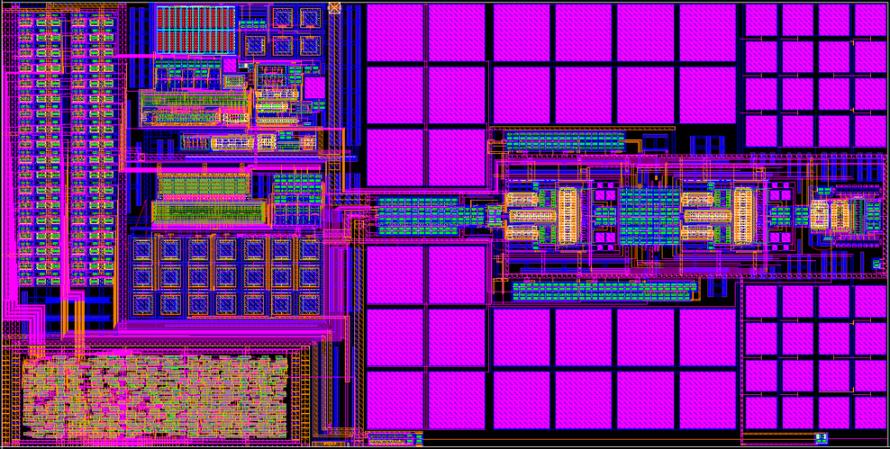

经过反复的检测与优化,最终会呈现出如下的电路图。

或者是这样:

这就是版图,包括了平面几何形状、文本标签等与物理布局相关的信息,通常是一个图形数据库系统(graphic data system,GDSⅡ)文件。

图中,我们可以清晰地看到蓝、红、绿、黄等不同色彩的区域,这些色彩区域分别对应着不同的光掩模版(后面会说,芯片制造篇也提到过)。

· 寄生参数提取和信号完整性分析

物理布局完成之后,又要开始进行验证了。

导线本身的电阻、相邻导线间的互感及耦合电容等因素(寄生参数),会在芯片内部引发信号噪声、串扰和反射等问题,导致信号电压发生波动甚至失真。

因此,需要进行寄生参数的提取,以及信号完整性的分析验证。

· 静态时序分析

在电路的每个单元位置和各项参数都已确定的情况下,需要再次进行静态时序分析,以确保结果的准确性。

· 形式验证

和前面一样。再做一次,确认一下电路功能是否与之前保持一致。

· 后仿真(时序仿真)

后仿真,也叫时序仿真。

它是在物理布局完成后进行,通过注入实际物理参数(如延时、寄生效应),验证芯片在真实工艺条件下的时序、功耗及信号完整性,确保设计可制造且可靠。

后仿真的核心关注点在时序验证、物理效应分析以及设计收敛。

时序验证前面说过,是检查建立时间(Setup Time)、保持时间(Hold Time)是否满足,避免信号竞争、毛刺等问题。

物理效应分析,是评估信号完整性(如串扰、噪声)、功耗热点及电压降。

设计收敛,是确保芯片在目标频率下稳定工作(如时钟边沿能否正确触发寄存器)。

前仿真和后仿真的对比,如下表所示:

· 物理验证

物理验证,主要包括LVS、DRC、ERC等检查,目的是确保版图的正确性和一致性。

LVS(Layout vs. Schematic):版图对原理图一致性检查,就是版图与逻辑综合后的门级电路图的对比验证。

DRC(Design Rule Checking):版图设计规则检查,检查连线间距,连线宽度等是否满足工艺要求。规则通常都由晶圆厂提供,确保设计在制造过程中不会出现物理上的问题,例如短路、开路、间距不足等。

ERC(Electrical Rue Checking):电气规则检查,检查短路和开路等电气规则违例。

· 功耗分析

功耗分析是确保芯片性能(Performance)、功耗(Power)和面积(Area)(简称PPA)平衡的核心环节。

它其实贯穿于芯片设计的整个流程,在前面我们也有提到相关流程。它的两大任务是分析IR drop(电压降)和EM(电迁移),防止因此导致的芯片失效。

功耗分析的核心方法包括静态功耗分析和动态功耗分析,常用工具包括Ansys公司的Redhawk,Cadence公司的Voltus,以及Synopsys公司的Ptpx。

· 工程变更

芯片设计有时候还会进行工程变更(Engineering Change Order,ECO)。

也就是局部修改单元位置或布线,解决STA或后仿真发现的违例问题。通过工程变更,可以避免重新设计。

· 签核

注意!布局布线完成后的这几个步骤,包括物理验证、静态时序分析、功耗和可靠性分析等,都属于签核(Sign-off)检查。

签核是流片前的最后一道“守门关”。

如果不满足,就要回到物理设计做修改。如果还是不满足,就需要返到电路设计和验证环节。

如果全都满足,那这个版图就可以送去晶圆厂流片。

签核也要采用EDA工具,包括了IR分析签核工具、时序分析签核工具、物理验证签核工具等。

对于目前越来越复杂的工艺,实现签核收敛(即所有检查均通过)变得越来越困难。这主要是因为多种物理效应(如工艺偏差OCV、信号完整性SI、电源完整性PI、热效应等)之间存在复杂的相互作用。

因此,签核工具需要具备更精确的建模能力、更全面的分析功能,并且常常需要AI的辅助来加速分析和收敛过程。

以上,就是后端设计的主要流程。在实际项目中,其实还包括了附加流程,例如填充单元插入,以及随着制造工艺不断演进产生的DFM(可制造性设计)等。大家有兴趣可以另外研究。

后端设计几个主要阶段的输入和输出,如下表所示:

后端设计全部完成之后,就可以输出最终的GDSⅡ文件了。文件包含以下信息:

层次结构和顶层结构:芯片的不同层和顶层结构,包括金属层、多晶硅层、掩膜层、胶片层等。

几何信息:包括芯片各个部位的尺寸、形状、位置以及与其他部位的连接方式等。

特殊功能区域:如联排、防抖动区域、纹理区、DPJ (Diffusion Pocket Junction) 等。

材料属性信息:描述每个层的材料类型、介电常数、厚度等。

█ 流片

最后,就是流片(Tape-out)!

物理版图以GDSⅡ的文件格式交给晶圆厂,就要开始流片,也就是试生产,制造几十片的样片。

流片为什么会叫Tape-out呢?

因为在上世纪七八十年代,芯片的设计数据都是写到磁带或者胶片里传给工厂。设计团队将数据写入磁带,叫Tape in。工厂读取磁带的数据,叫Tape out。随着时间的推移,磁带早已不用了,但是这个叫法一直沿用了下来。

晶圆厂拿到GDSⅡ文件,开始制作光刻掩模版(mask)。

光刻掩模版

光刻掩模版的制造过程和芯片晶圆的制造过程有点像,大概是这样的:

1、借助无掩模光刻机读取GDSⅡ版图文件,对涂有光刻胶的空白掩膜版进行非接触式曝光。这个步骤将照射掩膜版上预先设定的图形区域,引发光刻胶的光化学反应。

2、经过显影和定影处理后,曝光区域的光刻胶将溶解并脱落,从而暴露出下方的铬层。

3、采用铬刻蚀液进行湿法刻蚀,将暴露的铬层刻蚀掉,以形成透光区域。同时,受光刻胶保护的部分铬层则得以保留,从而形成不透光区域。

4、对掩膜版进行彻底清洗。这样,掩膜版上便形成了具有不同透光率的平面图形结构。

基于掩模版,制作芯片。然后,芯片设计企业对芯片进行详细的测试,看是否流片成功。

如果成功,那就congratulations!如果失败,就要评估能不能降级使用。如果不能,那就要么砸钱重来,要么宣告放弃!

资讯热榜 换一批

- 1 全网首拆!深度拆小米YU7四合一域控模块——深度分析英伟达Thor智驾域控

- 2 霍尔、AMR、GMR、TMR的对比解析及技术趋势

- 3 国产MEMS IMU势力崛起:盘点10家核心企业

- 4 心率血氧传感器全解析:PPG、ECG国产化技术突破及趋势

- 5 固态激光雷达:助力机器人技术升级

- 6 MEMS气体传感器全解析:技术原理、创新突破、未来趋势

- 7 解析全球13家领先柔性压力传感器制造商

- 8 OCP2137-为AMOLED显示屏量身定制的高效电源管理芯片

- 9 IMU深度解析:惯性测量单元的工作原理、应用、新品和选择指南

- 10 利润暴增165%!安防复苏,运动相机、AI眼镜表现亮眼,三大CMOS传感器厂商中报分析

免责声明

- 1、本文内容版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系感算商城(service@gansuan.com),我方将及时处理。

- 2、本文的引用仅供读者交流学习使用,不涉及商业目的。

- 3、本文内容仅代表作者观点,感算商城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

- 4、如需转载本方拥有版权的文章,请联系感算商城(service@gansuan.com)注明“转载原因”。未经允许私自转载感算商城将保留追究其法律责任的权利。